Since the serial port has a wide range of applications in telegraph communication, industrial control and data acquisition, most embedded processors have built-in Universal Asynchronous Receiver Transmitter (UART). UART data transmission is mainly realized by means of interrupt or DMA.

The interrupt mode is to generate an interrupt when receiving data or when data needs to be sent. The UART buffer (FIFO) is read and written in the interrupt service program to implement data transmission. Since the serial communication rate is generally low (typically no more than 115 200 bps), most embedded systems use interrupt mode to transmit serial data. However, the interrupt service routine needs to occupy the CPU time, and the increase of the serial port speed will also cause the CPU to respond to the UART interrupt more frequently, which will inevitably lead to the performance degradation of the embedded system.

DMA data transfer requires no CPU involvement and is a more efficient way to transfer data. Existing DMA data transmission schemes are based on DMA block transmission (ie, BLOCk DMA). In this way, a DMA interrupt is generated each time a block of data is transferred. In high-speed serial communication, frequent DMA interrupts still affect system performance. In this paper, based on the transmission mode of DMA (seatter DMA), a complete industrial high-speed serial port driver design scheme is proposed, which realizes UART data transmission with baud rate up to 12 Mbps.

2 characteristics of DMA data transmissionDMA (Direct Memory ACCess) refers to the direct transfer of data between memory and I/O devices. Data operations are performed by the DMA controller (DMAC) without the involvement of the CPU, greatly improving CPU utilization. . Therefore, DMA is an ideal way for high speed data transmission. Pay attention to the following points when using DMA for data transmission:

1 DMA transfer requires the use of the system bus, during which the CPU cannot use the bus. If the peripheral does not have any discontinuities in data transfer, it must ensure that the DMAC is exclusive to the system bus during the transfer, which may affect other devices that need to use the bus for data transfer. Therefore, whether the system bus can be preempted during DMA transfer depends on the specific environment of the embedded system.

2 DMA transfers have cache coherency issues. As shown in Figure 1, the DMAC and the CPU are two parallel units. The CPU always accesses the data in memory through the data cache, while the DMAC directly accesses the memory. If the data in memory is updated by the DMAC and the data in the data cache has not been updated, the value of some of the addresses obtained by the CPU may not be the actual value in memory. To avoid this problem, the data cache can be refreshed after the DMAC has updated the memory data or before the CPU reads the updated data, or a non-cacheable memory region that is not mapped by the data cache.

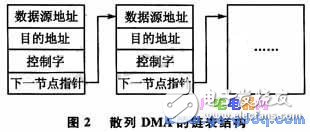

DMA data transmission can be divided into two ways: block transmission and hash transmission. In the process of DMA transfer of data, the source physical address and the target physical address must be contiguous. However, in some computer systems (such as the IA architecture), consecutive memory addresses are not necessarily contiguous physically, so DMA transfers are divided into multiple completions. After transmitting a piece of physically contiguous data, an interrupt is generated, and then the next piece of physically continuous data transfer is performed. This is the DMA block transfer mode (Block DMA). Hash transmission is developed in the block transfer mode, which is related to a transport chain table, as shown in Figure 2. The linked list can be a unidirectional structure or a ring structure. The control word contains control information such as the data bit width, the data block size, and whether the current block transfer end causes an interrupt. A DMA block transfer can be thought of as having only one node, and the next node pointer always points to the hash transfer of the current node. The hash DMA method enables more flexible and efficient data transfer.

Silicon Controlled Rectifier (SCR)

Silicon Controlled Rectifier (SCR) is short for silicon controlled rectifier. SCRs are available in one-way, two-way, turn-off, and light control types. It has the advantages of small size, light weight, high efficiency, long life, easy control, etc. It is widely used in occasions such as controllable rectification, voltage regulation, inverter, and non-contact switches and other automatic control and high-power electric energy conversion.

Silicon Controlled Rectifier,Scr Silicon Controlled Rectifier,3 Phase Silicon Controlled Rectifier,Semiconductor Silicon Controlled Rectifier

YANGZHOU POSITIONING TECH CO., LTD. , https://www.cndingweitech.com